Sigasi® Visual HDL™Want to manage Verilog and VHDL specifications with ease? Sigasi® Visual HDL™ transforms your VS Code workspace into a powerful HDL platform, simplifying and accelerating your workflow. Use it to design with real-time assistance and introspection. You can easily import existing code—whether from legacy projects, HLS- or AI-generated — and check it and the rest of your project for system and device-based insights. Get instantaneous results on rules in line with functional safety standards (STARC, DO-254, ISO 26262, and the like) or verification methodologies available through UVM, OSVVM, or VUnit. Resolve issues in your designs faster than ever with dynamic (UVM) block and state machine diagrams. Reveal, visualize, and explore the UVM testbench you have in mind. Intuitively discover the connections between ports, the relationships between components, and the topological arrangement using the new UVM Diagram. Navigate effortlessly between diagram and code, digging deeper into the hierarchy as needed, swiftly jumping to declarations, instantiations, and types. Play with full functionality using our completely free-of-charge Community Edition, as long as your designs have no commercial purposes. It requires Talkback, so you’ll lose your Sigasi functionality when you lose your internet connection (whether through your ISP or your own firewall). Do you need to work on a commercial project or do a commercial evaluation? No problem! Our Sales Team will be happy to discuss your options. You can always get in touch with our Support or Sales teams via email or our online form.

PrerequisitesEnsure you have a valid Sigasi Designer, Professional, or Enterprise license before starting the extension. Getting StartedSet the license in the extension settings, File > Preferences > Settings then search for Depending on how your project was set up, you should follow one of the following steps:

Afterwards, the

Project SetupThe

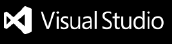

Project ConfigurationYou can configure project-specific settings by right-clicking on the project folder in the

Features that will improve your HDL design experienceCode CompletionOur powerful language server will offer smart suggestions for your HDL code as you type or by pressing

Code FormattingFormat your code to keep it clean and consistent. We worry about how it looks, so you can focus on designing.

You can easily use it by pressing

Find ReferencesFind where an identifier is used, anywhere in your design.

You can quickly access this by pressing

Design Hierarchy ViewSelect your top level and browse your design's hierarchy.

HoversJust hover your mouse over an identifier to see useful information about any part of your HDL design. For SystemVerilog macros, you can even see the expanded code. Hovers also allow you to quickly perform common actions.

Mark OccurrencesClick on an identifier to highlight all its usages in the current file.

NavigationNavigating through your complex design was never this easy. A simple

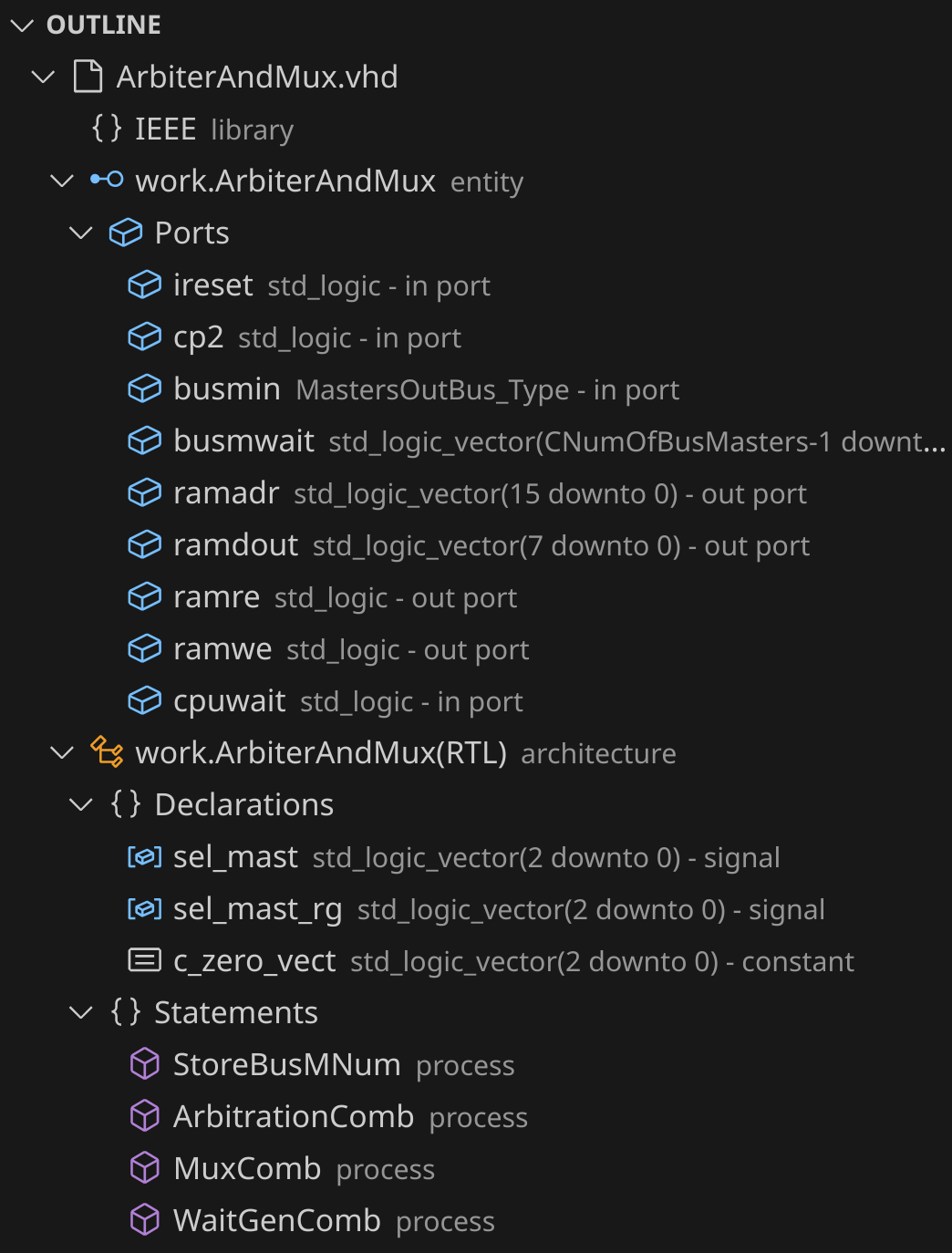

OutlineIn the outline, you can see everything that is defined in your file in a very compact and concrete way. Click one of the items to jump to it in your file. You can also enable

Preprocessor View for SystemVerilogThis view shows a fully expanded (preprocessed) SystemVerilog file.

Block DiagramDisplays a diagram of all architectures, modules, and their instantiations in your current VHDL or SystemVerilog editor. This diagram will automatically update while you are editing your code.

State Machines DiagramShows a diagram of state machines in your VHDL or SystemVerilog code from your current editor. This diagram will automatically update while you are editing your code.

Dependencies DiagramWith this diagram, you can visualize the dependencies of your VHDL, SystemVerilog, or mixed-language projects.

Documentation ExportExport the generated documentation in HTML for a project or a top level.

RenameRename allows you to change the name of an identifier across your whole design, this is perfect when you want to change the name of a signal throughout your design.

You can rename something by pressing

Have a question or suggestion?We greatly appreciate feedback from our users, so don't hesitate to contact our support at support+vscode@sigasi.com Explore many more features and documentation in the manual FAQHow do I set up my project?See our Prerequisites and Getting Started sections. |